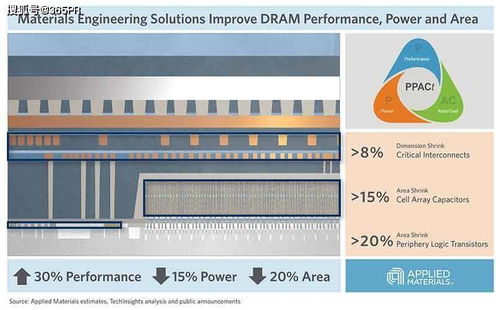

新材料工程方案 突破DRAM电容器微缩瓶颈,加速物联网与计算机网络工程融合

随着物联网(IoT)设备数量的指数级增长和计算机网络工程对高性能、低功耗计算的持续需求,动态随机存取存储器(DRAM)作为核心存储部件,其性能与能效比直接影响到整个系统的响应速度与续航能力。在工艺节点不断微缩的进程中,DRAM电容器的物理极限已成为制约其进一步发展的关键瓶颈。传统的电容器材料与结构在纳米尺度下,面临着电荷存储能力下降、漏电流增大、可靠性降低等一系列严峻挑战。本文将探讨几种前沿的材料工程解决方案,这些方案旨在有效加速DRAM电容器的微缩进程,从而为更高效、更密集的物联网终端与网络设备铺平道路。

一、挑战:DRAM电容器微缩的核心难题

DRAM的基本存储单元由一个晶体管和一个电容器组成。电容器负责存储电荷(代表数据位“1”或“0”)。随着制程工艺从几十纳米向个位数纳米迈进,电容器所占用的面积急剧缩小。根据电容公式 C = εA/d(C为电容量,ε为介电常数,A为电极面积,d为介质厚度),在面积A被迫减小的为了维持足够高的电容值以确保数据读取的可靠性和抗干扰能力(通常需要约25-30 fF/单元),传统思路是减薄介质厚度d或寻找更高ε(介电常数)的材料。介质过薄会导致量子隧穿效应加剧,漏电流激增,数据刷新频率加快,功耗显著上升,这与物联网设备低功耗的核心诉求背道而驰。

二、材料工程解决方案

为破解上述难题,材料科学与工程领域提出了多维度创新方案:

1. 高介电常数(高κ)介电材料的开发与应用

这是最直接的路径。用高κ材料(如Al2O3、HfO2、ZrO2及其叠层或掺杂化合物)替代传统的SiO2或Si3N4/SiO2复合介质,可以在不增加物理厚度或减小面积的情况下,实现更高的单位面积电容。例如,掺杂稀土元素(如La、Y)的HfO2薄膜可以显著提升其κ值并优化结晶性,从而在更小的尺寸下保持优异的绝缘性能和存储电荷能力。这直接支持了DRAM向更小制程节点的演进,为集成度更高的物联网芯片奠定基础。

2. 三维电容器结构的材料与工艺创新

当平面(2D)面积受限时,向第三维度拓展是必然选择。深沟槽(Deep Trench)和柱状(Cylindrical)等3D电容器结构通过增加电极的侧壁面积来有效提升总电容。此路径的成功高度依赖于材料工程:

- 电极材料:需要开发具有高表面积、优异导电性及与高κ介质良好界面特性的电极材料。例如,使用原子层沉积(ALD)技术制备的TiN、Ru、RuO2等金属或金属氮化物电极,能完美共形地覆盖在复杂3D结构的表面。

- 介质沉积技术:ALD技术因其卓越的台阶覆盖能力、原子级厚度控制和高均匀性,成为在3D结构上沉积高κ介质层的不二之选。精确的ALD工艺工程确保了纳米级深宽比结构内部介质层的均匀性与可靠性。

3. 铁电材料的复兴与集成(FeDRAM)

这是一项潜在的颠覆性技术。基于铪基(如HfO2掺杂Zr)的铁电材料,在纳米尺度下仍能表现出稳定的铁电性。铁电电容器利用自发极化存储数据,其电容值(在特定偏压下)可远高于传统线性介质,且具有非易失性潜质。将铁电材料集成到DRAM电容器中(形成FeDRAM),有望在微缩的同时大幅降低刷新功耗,这对于始终在线、对功耗极度敏感的物联网传感器节点意义重大。其耐久性(极化翻转次数)和工艺集成仍是当前材料工程研究的焦点。

4. 界面工程与缺陷控制

在纳米尺度下,介质与电极之间的界面特性以及介质薄膜内部的缺陷(如氧空位)对漏电流和可靠性有决定性影响。通过等离子体处理、界面插入层(如Al2O3薄层)、以及前驱体化学和沉积工艺的精确调控,可以钝化界面、减少缺陷态密度,从而在实现高电容的将漏电流控制在可接受范围内。

三、对物联网与计算机网络工程的意义

这些材料工程的进步,将具体转化为以下系统级优势:

- 更高的存储密度与带宽:更小的DRAM单元意味着在同等芯片面积内可以集成更多存储单元,或是在保持容量的前提下显著缩小芯片尺寸。这对于空间受限的物联网终端(如可穿戴设备、智能传感器)至关重要。高密度DRAM支持更快的数据存取速率,提升了边缘计算设备的处理能力,缓解了计算机网络中的数据拥塞。

- 更低的功耗:通过高κ材料、3D结构或铁电材料实现足够的单元电容,可以降低工作电压或减少刷新频率,直接降低动态功耗和待机功耗。这极大地延长了物联网设备的电池寿命,并降低了数据中心等网络基础设施的运营成本。

- 增强的系统可靠性:优化的材料与界面带来了更稳定的电气性能和更长的数据保持时间,提高了在复杂或恶劣网络环境中运行的物联网设备的可靠性。

结论

DRAM电容器的微缩已不再仅仅是几何尺寸的缩小,更是一场深入原子层面的材料工程革命。通过协同创新高κ介质、3D集成技术、铁电材料以及精密界面控制,我们正在有效突破物理极限,推动DRAM技术持续向前发展。这些材料解决方案的成功实施,将为下一代物联网海量连接与实时数据处理,以及高速、智能的计算机网络工程,提供强大而高效的核心存储基石,加速万物智能互联时代的全面到来。

如若转载,请注明出处:http://www.hmbqs.com/product/17.html

更新时间:2026-04-16 23:02:55